| K.1 | Introduction                                                     | K-2  |

|-----|------------------------------------------------------------------|------|

| K.2 | A Survey of RISC Architectures for Desktop, Server, and Embedded |      |

|     | Computers                                                        | K-3  |

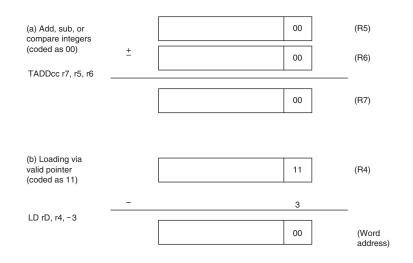

| K.3 | The Intel 80x86                                                  | K-30 |

| K.4 | The VAX Architecture                                             | K-50 |

| K.5 | The IBM 360/370 Architecture for Mainframe Computers             | K-69 |

| K.6 | Historical Perspective and References                            | K-75 |

# Κ

# Survey of Instruction Set Architectures

RISC: any computer announced after 1985.

**Steven Przybylski** A Designer of the Stanford MIPS

# K.1 Introduction

This appendix covers 10 instruction set architectures, some of which remain a vital part of the IT industry and some of which have retired to greener pastures. We keep them all in part to show the changes in fashion of instruction set architecture over time.

We start with eight RISC architectures, using RISC V as our basis for comparison. There are billions of dollars of computers shipped each year for ARM (including Thumb-2), MIPS (including microMIPS), Power, and SPARC. ARM dominates in both the PMD (including both smart phones and tablets) and the embedded markets.

The 80x86 remains the highest dollar-volume ISA, dominating the desktop and the much of the server market. The 80x86 did not get traction in either the embedded or PMD markets, and has started to lose ground in the server market. It has been extended more than any other ISA in this book, and there are no plans to stop it soon. Now that it has made the transition to 64-bit addressing, we expect this architecture to be around, although it may play a smaller role in the future then it did in the past 30 years.

The VAX typifies an ISA where the emphasis was on code size and offering a higher level machine language in the hopes of being a better match to programming languages. The architects clearly expected it to be implemented with large amounts of microcode, which made single chip and pipelined implementations more challenging. Its successor was the Alpha, a RISC architecture similar to MIPS and RISC V, but which had a short life.

The vulnerable IBM 360/370 remains a classic that set the standard for many instruction sets to follow. Among the decisions the architects made in the early 1960s were:

- 8-bit byte

- Byte addressing

- 32-bit words

- 32-bit single precision floating-point format + 64-bit double precision floatingpoint format

- 32-bit general-purpose registers, separate 64-bit floating-point registers

- Binary compatibility across a family of computers with different costperformance

- Separation of architecture from implementation

As mentioned in Chapter 2, the IBM 370 was extended to be virtualizable, so it had the lowest overhead for a virtual machine of any ISA. The IBM 360/370 remains the foundation of the IBM mainframe business in a version that has extended to 64 bits.

# A Survey of RISC Architectures for Desktop, Server, and Embedded Computers

#### Introduction

K.2

We cover two groups of Reduced Instruction Set Computer (RISC) architectures in this section. The first group is the desktop, server RISCs, and PMD processors:

- Advanced RISC Machines ARMv8, AArch64, the 64-bit ISA,

- MIPS64, version 6, the most recent the 64-bit ISA,

- Power version 3.0, which merges the earlier IBM Power architecture and the PowerPC architecture.

- RISC-V, specifically RV64G, the 64-bit extension of RISC-V.

- SPARCv9, the 64-bit ISA.

As Figure K.1 shows these architectures are remarkably similar.

There are two other important historical RISC processors that are almost identical to those in the list above: the DEC Alpha processor, which was made by Digital Equipment Corporation from 1992 to 2004 and is almost identical to MIPS64. Hewlett-Packard's PA-RISC was produced by HP from about 1986 to 2005, when it was replaced by Itanium. PA-RISC is most closely related to the Power ISA, which emerged from the IBM Power design, itself a descendant of IBM 801.

The second group is the embedded RISCs designed for lower-end applications:

- Advanced RISC Machines, Thumb-2: an 32-bit instruction set with 16-bit and 32-bit instructions. The architecture includes features from both ARMv7 and ARMv8.

- microMIPS64: a version of the MIPS64 instruction set with 16-it instructions, and

- RISC-V Compressed extension (RV64GC), a set of 16-bit instructions added to RV64G

Both RV64GC and microMIPS64 have corresponding 32-bit versions: RV32GC and microMIPS32.

Since the comparison of the base 32-bit or 64-bit desktop and server architecture will examine the differences among those ISAs, our discussion of the embedded architectures focuses on the 16-bit instructions. Figure K.2 shows that these embedded architectures are also similar. In all three, the 16-bit instructions are versions of 32-bit instructions, typically with a restricted set of registers. The idea is to reduce the code size by replacing common 32-bit instructions with 16-bit versions. For RV32GC or Thumb-2, including the 16-bit instructions yields a reduction in code size to about 0.73 of the code size using only the 32-bit ISA (either RV32G or ARMv7).

|                                            | ARMv8                                          | MIPS64 R6                                | Power v3.0                               | RV64G                                    | SPARCv9                                  |

|--------------------------------------------|------------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|

| Original date (base ISA)                   | 1986                                           | 1986                                     | 1990                                     | 2016                                     | 1987                                     |

| Date of this ISA                           | 2011                                           | 2014                                     | 2013                                     | 2016                                     | 2008                                     |

| Instruction size (bits)                    | 32                                             | 32                                       | 32                                       | 32                                       | 32                                       |

| Address space (size, model)                | 64 bits (flat)                                 | 64 bits, flat                            | 64 bits, flat                            | 64 bits, flat                            | 64 bits, flat                            |

| Data alignment                             | Aligned preferred                              | Aligned preferred                        | Unaligned                                | Aligned<br>preferred                     | Aligned                                  |

| Data addressing modes                      | 8 (including<br>scaled, pre/post<br>increment) | 1 (+1 for FP<br>only)                    | 4                                        | 1                                        | 2                                        |

| Integer registers (number,<br>model, size) | 31 GPR x 64,<br>plus stack<br>pointer          | 31 GPR<br>× 64 bits                      | 31 GPR<br>× 64 bits                      | 31 GPR<br>×64 bits                       | 31 GPR<br>× 64 bits                      |

| Separate floating-point registers          | 32x32 or 32x64<br>bits                         | $32 \times 32$ or<br>$32 \times 64$ bits |

| Floating-point format                      | IEEE 754<br>single, double                     | IEEE 754 single,<br>double               | IEEE 754<br>single, double               | IEEE 754<br>single, double               | IEEE 754<br>single, doubl                |

**Figure K.1** Summary of the most recent version of five architectures for desktop, server, and PMD use (all had earlier versions). Except for the number of data address modes and some instruction set details, the integer instruction sets of these architectures are very similar. Contrast this with Figure K.29. In ARMv8, register 31 is a 0 (like register 0 in the other architectures), but when it is used in a load or store, it is the current stack pointer, a special purpose register. We can either think of SP-based addressing as a different mode (which is how the assembly mnemonics operate) or as simply a register + offset addressing mode (which is how the instruction is encoded).

|                                                                                        | microMIPS64                                                   | RV64GC                                  | Thumb-2                 |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------|-------------------------|

| Date announced                                                                         | 2009                                                          | 2016                                    | 2003                    |

| Instruction size (bits)                                                                | 16/32                                                         | 16/32                                   | 16/32                   |

| Address space (size, model)                                                            | 32/64 bits, flat                                              | 32/64 bits flat                         | 32 bits, flat           |

| Data alignment                                                                         | Aligned                                                       | Aligned, preferred                      | Aligned                 |

| Data addressing modes                                                                  | 2                                                             | 1                                       | 6                       |

| Integer registers (number, model, size)                                                | 31 GPR $\times$ 64 bits                                       | $31 \text{ GPR} \times 64 \text{ bits}$ | 15 GPR $\times$ 32 bits |

| Integer registers accessible by most 16-bit instructions (which use should specifiers) | 8 GPR + SP + GP<br>+RA<br>GPRs: 0, 2-7, 17,<br>or 2-7, 16, 17 | 8 GPRs + SP<br>GPRs: 8-15               | 8 GPR + SP × 32 bits    |

**Figure K.2** Summary of three recent architectures for embedded applications. All three use 16-bit extensions of a base instruction set. Except for number of data address modes and a number of instruction set details, the integer instruction sets of these architectures are similar. Contrast this with Figure K.29. An earlier 16-bit version of the MIPS instruction set, called MIPS16, was created in 1995 and was replaced by microMIPS32 and microMIPS64. The first Thumb architecture had only 16-bit instructions and was created in 1996. Thumb-2 is built primarily on ARMv7, the 32-bit ARM instruction set; it offers 16 registers. RISC-V also defines RV32E, which has only 16 registers, includes the 16-bit instructions, and cannot have floating point. It appears that most implementations for embedded applications opt for RV32C or RV64GC.

A key difference among these three architectures is the structure of the base 32-bit ISA. In the case of RV64GC, the 32-bit instructions are exactly those of RV64G. This is possible because RISC V planned for the 16-it option from the beginning, and branch addresses and jump addresses are specified to 16-it boundaries. In the case of microMIPS64, the base ISA is MIPS64, with one change: branch and jump offsets are interpreted as 16-bit rather than 32-bit aligned. (microMIPS also uses the encoding space that was reserved in MIPS64 for user-defined instruction set extensions; such extensions are not part of the base ISA.)

Thumb-2 uses a slightly different approach. The 32-bit instructions in Thumb-2 are mostly a subset of those in ARMv7; certain features that were dropped in ARMv8 are not included (e.g., conditional execution of most instructions and the ability to write the PC as a GPR). Thumb-2 also includes a few dozen instructions introduced in ARMv8, specifically bit field manipulation, additional system instructions, and synchronization support. Thus, the 32-bit instructions in Thumb-2 constitute a unique ISA.

Earlier versions of the 16-bit instruction sets for MIPS (MIPS16) and ARM (Thumb), took the approach of creating a separate mode, invoked by a procedure call, to transfer control to a code segment that employed only 16-bit instructions.

The 16-bit instruction set was not complete and was only intended for user programs that were code-size critical.

One complication of this description is that some of the older RISCs have been extended over the years. We decided to describe the most recent versions of the architectures: ARMv8 (the 64-bit architecture AArch64), MIPS64 R6, Power v3.0, RV64G, and SPARC v9 for the desktop/server/PMD, and the 16-bit subset of the ISAs for microMIPS64, RV64GC, and Thumb-2.

The remaining sections proceed as follows. After discussing the addressing modes and instruction formats of our RISC architectures, we present the survey of the instructions in five steps:

- Instructions found in the RV64G core, described in Appendix A.

- Instructions not found in the RV64G or RV64GC but found in two or more of the other architectures. We describe and organize these by functionality, e.g. instructions that support extended integer arithmetic.

- Instruction groups unique to ARM, MIPS, Power, or SPARC, organized by function.

- Multimedia extensions of the desktop/server/PMD RISCs

- Digital signal-processing extensions of the embedded RISCs

Although the majority of the instructions in these architectures are included, we have not included every single instruction; this is especially true for the Power and ARM ISAs, which have *many* instructions.

### Addressing Modes and Instruction Formats

Figure K.3 shows the data addressing modes supported by the desktop/server/ PMD architectures. Since all, but ARM, have one register that always has the value 0 when used in address modes, the absolute address mode with limited range can be synthesized using register 0 as the base in displacement addressing. (This register can be changed by arithmetic-logical unit (ALU) operations in PowerPC, but is always zero when it is used in an address calculation.) Similarly, register indirect addressing is synthesized by using displacement addressing with an offset of 0. Simplified addressing modes is one distinguishing feature of RISC architectures.

As Figure K.4 shows, the embedded architectures restrict the registers that can be accessed with the 16-bit instructions, typically to only 8 registers, for most instructions, and a few special instructions that refer to other registers. Figure K.5 shows the data addressing modes supported by the embedded architectures in their 16-bit instruction mode. These versions of load/store instructions restrict the registers that can be used in address calculations, as well as significantly shorten the immediate fields, used for displacements.

References to code are normally PC-relative, although jump register indirect is supported for returning from procedures, for case statements, and for pointer function calls. One variation is that PC-relative branch addresses are often shifted left 2 bits before being added to the PC for the desktop RISCs, thereby increasing the branch distance. This works because the length of all instructions for the desktop

|                                                                                  | ARMv8      | MIPS64 R6  | Power v3.0 | RV64G      | SPARCv9    |

|----------------------------------------------------------------------------------|------------|------------|------------|------------|------------|

| Register + offset (displacement or based)                                        | B, H, W, D |

| Register + register (indexed)                                                    | B, H, W, D |            | B, H, W, D |            | B, H, W, D |

| Register + scaled register (scaled)                                              | B, H, W, D | W,D        |            |            |            |

| Register + register + offset                                                     | B, H, W, D |            |            |            |            |

| Register + offset & update register to effective address (based with update)     | B, H, W, D |            | B, H, W, D |            |            |

| Register & update register to register +<br>offset (register with update)        | B, H, W, D |            |            |            |            |

| Register + Register & update register to effective address (indexed with update) | B, H, W, D |            | B, H, W, D |            |            |

| PC-relative (PC + displacement)                                                  | W, D       | W, D       |            |            |            |

**Figure K.3** Summary of data addressing modes supported by the desktop architectures, where B, H, W, D indicate what datatypes can use the addressing mode. Note that ARM includes two different types of address modes with updates, one of which is included in Power.

#### K.2 A Survey of RISC Architectures for Desktop, Server, and Embedded Computers **K-7**

| Register specifier      | microMIPS64                                   | RV64GC                      | Thumb-2                        |

|-------------------------|-----------------------------------------------|-----------------------------|--------------------------------|

| 3-bit                   | 2-7,16, 17                                    | 8-15                        | 0-7                            |

| stack pointer register  | 29                                            | 2                           | 0 (when used in load/store)    |

| global pointer register | 28                                            |                             |                                |

| return address register | 31                                            | 1                           | 14                             |

| Using special register  | stack pointer or global pointer; 5-bit offset | stack pointer; 5-bit offset | stack pointer; 8-bit<br>offset |

**Figure K.4** Register encodings for the 16-bit subsets of microMIPS64, RV64GC, and Thumb-2, including the core general purpose registers, and special-purpose registers accessible by some instructions.

| Addressing mode                           | microMIPS64                                   | RV64GC                              | Thumb-2                             |

|-------------------------------------------|-----------------------------------------------|-------------------------------------|-------------------------------------|

| Register + offset (displacement or based) | 4-bit offset, one of 8 registers              | 5-bit offset, one of 8<br>registers | 5-bit offset, one of 8<br>registers |

| PC-relative data                          |                                               |                                     | word only; 8-bit offset             |

| Using special register                    | stack pointer or global pointer; 5-bit offset | stack pointer; 5-bit<br>offset      | stack pointer; 8-bit<br>offset      |

**Figure K.5** Summary of data addressing modes supported by the embedded architectures. microMIPS64, RV64c, and Thumb-2 show only the modes supported in 16-bit instruction formats. The stack pointer in RV64GC and micro-MIPS64 is a designed GPR; it is another version of r31 is Thumb-2. In microMIPS64, the global pointer is register 30 and is used by the linkage convention to point to the global variable data pool. Notice that typically only 8 registers are accessible as base registers (and as we will see as ALU sources and destinations).

RISCs is 32 bits and instructions must be aligned on 32-bit words in memory. Embedded architectures and RISC V (when extended) have 16-bit-long instructions and usually shift the PC-relative address by 1 for similar reasons.

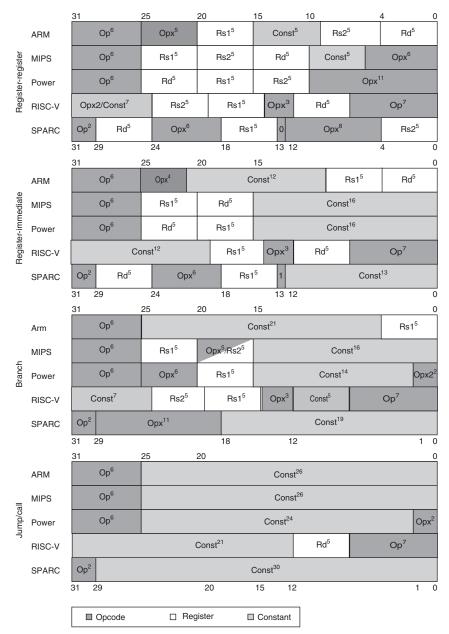

Figure K.6 shows the most important instruction formats of the desktop/server/ PMD RISC instructions. Each instruction set architecture uses four primary instruction formats, which typically include 90–98% of the instructions. The register-register format is used for register-register ALU instructions, while the ALU immediate format is used for ALU instructions with an immediate operand and also for loads and stores. The branch format is used for conditional branches, and the jump/call format for unconditional branches (jumps) and procedures calls.

There are a number of less frequently used instruction formats that Figure K.6 leaves out. Figure K.7 summarizes these for the desktop/server/PMD architectures.

Unlike, their 32-bit base architectures, the 16-bit extensions (microMIPS64, RV64GC, and Thumb-2) are focused on minimizing code. As a result, there are a larger number of instruction formats, even though there are far fewer instructions.

**K-8** Appendix K Survey of Instruction Set Architectures

| K.2 | A Survey of RISC | Architectures for | Desktop, | Server, and | Embedded | Computers |  | K-9 |

|-----|------------------|-------------------|----------|-------------|----------|-----------|--|-----|

|-----|------------------|-------------------|----------|-------------|----------|-----------|--|-----|

| Architecture | Additional<br>instruction<br>formats    | Format function and use                                                                                                         |

|--------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| ARMv8        | At least 10 (many                       | Logical immediates with 13-bit immediate field.                                                                                 |

|              | small variations);                      | Shifts with constant amount.(16-bit opcode)                                                                                     |

|              | major forms are<br>shown.               | 16-bit immediate form                                                                                                           |

|              | 5110 1011.                              | Exclusive operations: three register fields                                                                                     |

|              |                                         | Branch register: long opcode                                                                                                    |

|              |                                         | Load/store with address mode bits.                                                                                              |

| MIPS64       | 1                                       | A PC-relative set of load/stores using register-immediate format but with 18-bit immediates (since the other source is the PC). |

| Power        | 9 (not including a number of small      | DQ-mode: uses the ALU immediate form but takes four bits of the displacement for other functions.                               |

|              | variations or the<br>vector extensions) | DS-mode: uses the ALU immediate form but takes two bits of the displacement for other functions.                                |

|              |                                         | DX-form: Like register-immediate, but with a register-source replaced by PC.                                                    |

|              |                                         | MD, MDS formats: like register-register but used for shifts and rotates.                                                        |

|              |                                         | X, XS, and several minor variations: used for indexed addressing modes, shifts, and a variety of extended purposes.             |

|              |                                         | Z22, Z23 formats: used for manipulating floating point numbers                                                                  |

| RV64         | 2                                       | SB format: a variant of the branch format with different immediate treatment                                                    |

|              |                                         | UJ format: a variant of the jump/call format with different immediate treatment                                                 |

| SPARC        | 3                                       | Another format for conditional branches containing 3 more bits of displacement (22 total versus 19) but no prediction hints.    |

|              |                                         | A format with 22-bit immediate used to load the upper half of a register,                                                       |

|              |                                         | A format for conditional branches based on a register compare with zero.                                                        |

**Figure K.7** Other instruction formats beyond the four major formats of the previous figure. In some cases, there are formats very similar to one of the four core formats, but where a register field is used for other purposes. The Power architecture also includes a number of formats for vector operations.

microMIPs64 and RV64GC have eight and seven major formats, respectively, and Thumb-2 has 15. As Figure K.8 shows, these involve varying number of register operands (0 to 3), different immediate sizes, and even different size register specifiers, with a small number of registers accessible my most instructions, and fewer instructions able to access all 32 registers.

# Instructions

The similarities of each architecture allow simultaneous descriptions, starting with the operations equivalent to the RISC-V 64-bit ISA.

| Architecture | Opcode<br>main:<br>extended | Register<br>specifiers x<br>length | Immediate<br>field<br>length | Typical instructions                                                                                                                                                          |

|--------------|-----------------------------|------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| microMIPS64  | 6                           | none                               | 10                           | Jumps                                                                                                                                                                         |

|              | 6                           | 1x5                                | 5                            | Register-register operation (32 registers) and Load using SP as base register; any destination                                                                                |

|              | 6                           | 1x3                                | 7                            | Branches equal/not equal zero. Loads using GP. as base.                                                                                                                       |

|              | 6:4                         | 2x3                                |                              | Register-register operation, rd/rs1, and rs2; 8 registers                                                                                                                     |

|              | 6:1                         | 2x3                                | 3                            | Register-register immediate, rd/rs1, and rs2; 8 registers                                                                                                                     |

|              | 6                           | 2x3                                | 4                            | Loads and stores; 8 registers                                                                                                                                                 |

|              | 6:4                         | 2x3                                |                              | Register-register operation, rd, and rs1; 8 registers                                                                                                                         |

|              | 6                           | 2x5                                |                              | Register-register operation; 32 registers.                                                                                                                                    |

| RV64GC       | 2:3                         |                                    | 11                           | Jumps                                                                                                                                                                         |

|              | 2:3                         | 1x3                                | 7                            | Branch                                                                                                                                                                        |

|              | 2:3                         | 1x3                                | 8                            | Immediate one source register.                                                                                                                                                |

|              | 2:3                         | 1x5                                | 6                            | Store using SP as base.                                                                                                                                                       |

|              | 2:3                         | 1x5                                | 6                            | ALU immediate and load using SP as base.                                                                                                                                      |

|              | 2:4                         | 2x5                                |                              | Register-register operation                                                                                                                                                   |

|              | 2:3                         | 2x3                                | 5                            | Loads and stores using 8 registers.                                                                                                                                           |

| Thumb-2      | 3:2                         | 2x3                                | 5                            | Shift, move, load/store word/byte                                                                                                                                             |

|              | 3:2                         | 1x3                                | 8                            | immediates: add, subtract, move, and compare                                                                                                                                  |

|              | 4:1                         | 1x3                                | 8                            | Load/store with stack pointer as base, Add to SP or PC, Load/store multiple                                                                                                   |

|              | 4:3                         | 3x3                                |                              | Load register indexed                                                                                                                                                         |

|              | 4:4                         |                                    | 8                            | Conditional branch, system instruction                                                                                                                                        |

|              | 4:12                        |                                    |                              | Miscellaneous: 22 different instructions with 12 formats (includes compare and branch on zero, pop/push registers, adjust stack pointer, reverse bytes, IF-THEN instruction). |

|              | 5                           | 1x3                                | 8                            | Load relative to PC                                                                                                                                                           |

|              | 5                           |                                    | 11                           | Unconditional branch                                                                                                                                                          |

|              | 6:1                         | 3x3                                |                              | Add/subtract                                                                                                                                                                  |

|              | 6:3                         | 1x4, 1x3                           |                              | Special data processing                                                                                                                                                       |

|              | 6:4                         | 2x3                                |                              | Logical data processing                                                                                                                                                       |

|              | 6:6                         | 1x4                                |                              | Branch and change instruction set (ARM vs. Thumb)                                                                                                                             |

**Figure K.8** Instruction formats for the 16-bit instructions of microMIPS64, RV64GC, and Thumb-2. For instructions with a destination and two sources, but only two register fields, the instruction uses one of the registers as both source and destination. Note that the extended opcode field (or function field) and immediate field sometimes overlap or are identical. For RV64GC and microMIPS64, all the formats are shown; for Thumb-2, the Miscellaneous format includes 22 instructions with 12 slightly different formats; we use the extended opcode field, but a few of these instructions have immediate or register fields.

#### K.2 A Survey of RISC Architectures for Desktop, Server, and Embedded Computers **K-11**

#### **RV64G** Core Instructions

Almost every instruction found in the RV64G is found in the other architectures, as Figures K.9 through K.19 show. (For reference, definitions of the RISC-V instructions are found in Section A.9.) Instructions are listed under four categories: data transfer (Figure K.9); arithmetic, logical (Figure K.10); control (Figure K.11 and Figure K.12); and floating point (Figure K.13).

If a RV64G core instruction requires a short sequence of instructions in other architectures, these instructions are separated by semicolons in Figure K.9 through Figure K.13. (To avoid confusion, the destination register will always be the leftmost operand in this appendix, independent of the notation normally used with each architecture.).

#### Compare and Conditional Branch

Every architecture must have a scheme for compare and conditional branch, but despite all the similarities, each of these architectures has found a different way to perform the operation! Figure K.11 summarizes the control instructions, while Figure K.12 shows details of how conditional branches are handled. SPARC uses the traditional four condition code bits stored in the program status word: *negative*, zero, carry, and overflow. They can be set on any arithmetic or logical instruction; unlike earlier architectures, this setting is optional on each instruction. An explicit option leads to fewer problems in pipelined implementation. Although condition codes can be set as a side effect of an operation, explicit compares are synthesized with a subtract using r0 as the destination. SPARC conditional branches test condition codes to determine all possible unsigned and signed relations. Floating point uses separate condition codes to encode the EEE 754 conditions, requiring a floating-point compare instruction. Version 9 expanded SPARC branches in four ways: a separate set of condition codes for 64-bit operations; a branch that tests the contents of a register and branches if the value is =, not=, <, <=, >=, or <= 0; three more sets of floating-point condition codes; and branch instructions that encode static branch prediction.

Power also uses four condition codes: *less than, greater than, equal*, and *summary overflow*, but it has eight copies of them. This redundancy allows the Power instructions to use different condition codes without conflict, essentially giving Power eight extra 4-bit registers. Any of these eight condition codes can be the target of a compare instruction, and any can be the source of a conditional branch. The integer instructions have an option bit that behaves as if the integer is followed by a compare to zero that sets the first condition "register." Power also lets the second "register" be optionally set by floating-point instructions. PowerPC provides logical operations among these eight 4-bit condition code registers (CRAND, CROR, CRXOR, CRNAND, CRNOR, CREQV), allowing more complex conditions to be tested by a single branch. Finally, Power includes a set of branch count registers, that are automatically decremented when tested, and can be used in a branch condition. There are also special instructions for moving from/to the condition register.

#### **K-12** Appendix K Survey of Instruction Set Architectures

| Data transfer<br>(instruction formats) | R-I                           | R-I                             | R-I, R-R       | R-I                                                                                                              | R-I, R-R              |

|----------------------------------------|-------------------------------|---------------------------------|----------------|------------------------------------------------------------------------------------------------------------------|-----------------------|

| Instruction name                       | ARMv8                         | MIPS64                          | Power          | RV64G                                                                                                            | SPARC                 |

| Load byte signed/unsigned.             | LDR_B                         | LB_                             | LBZ;<br>EXTSB  | LB_                                                                                                              | LD_B                  |

| Load halfword signed,<br>unsigned      | LDR <u>H</u>                  | LH_                             | LHA/LHZ        | LH_                                                                                                              | LD_H                  |

| Load word                              | LDRSW/LDR                     | LW_                             | LW_            | LW_                                                                                                              | LD_W                  |

| Load double                            | LDRX                          | LD                              | LD             | LD                                                                                                               | LDD                   |

| Load float register SP/DP              | LD_                           | L_C1                            | LF_            | FL_                                                                                                              | LD_F                  |

| Store byte                             | STB                           | SB                              | STB            | SB                                                                                                               | STB                   |

| Store half word                        | STW                           | SH                              | STH            | STH                                                                                                              | STH                   |

| Store word                             | STL                           | SW                              | STW            | SW                                                                                                               | ST                    |

| Store double word                      | STX                           | SD                              | SD             | SD                                                                                                               | STD                   |

| Store float SP/DP                      | ST_                           | S_C1                            | STF_           | FS_                                                                                                              | ST_F                  |

| Load reserved                          | LDEXB,LDEXH<br>LDEXW,LDEXD    | LL, LLD                         | lwarx, ldarx,  | LR                                                                                                               |                       |

| Store conditional                      | STEXB, STEXH,<br>STEXW, STEXD | SC, SCD                         | stwcx, stdcx   | SC                                                                                                               |                       |

| Read/write spec. register              | MF_, MT_                      | MF, MT_                         | M_SPR,         | csrr_,<br>csrr_i,                                                                                                | RD,WR                 |

| Move integer to FP register            | ITOFS                         | MFC1/<br>DMFC1                  | STW; LDFS      | STW; FLDWX                                                                                                       | ST; LDF               |

| Move FP to integer register            | FTTOIS                        | MTC1/<br>DMTC1                  | STFS; LW       | FSTWX; LDW                                                                                                       | STF; LD               |

| Synchronize data, instruction stream   | DSB<br>ISB                    | SYNC,<br>SYNCI                  | SYNC,<br>ISYNC | Fence<br>Fence.i                                                                                                 | MEMBAR<br>FLUSH       |

| Atomic operations                      | LDWAT, LDDAT<br>STWAT, STDAT  | LLWP,<br>LLDP,<br>SCWP,<br>SCDP |                | AMOSWAP.W/D,<br>AMOADD,W.D,<br>AMOAND.W/D,<br>AMOXOR.W/D,<br>AMOOR.W/D,<br>AMOOR.W/D,<br>AMOMINW/D,<br>AMOMAXW/D | CASA, SWAP,<br>LDSTUB |

**Figure K.9 Desktop RISC data transfer instructions equivalent to RV64G core.** A sequence of instructions to synthesize a RV64G instruction is shown separated by semicolons. The MIPS and Power instructions for atomic operations load and conditionally store a pair of registers and can be used to implement the RV64G atomic operations with at most one intervening ALU instruction. The SPARC instructions: compare-and-swap, swap, LDSTUB provide atomic updates to a memory location and can be used to build the RV64G instructions. The Power3 instructions provide all the functionality, as the RV64G instructions, depending on a function field.

| Arithmetic/logical<br>(instruction formats)                                            | R-R, R-I       | R-R, R-I                    | R-R, R-I        | R-R, R-I                     | R-R, R-I         |

|----------------------------------------------------------------------------------------|----------------|-----------------------------|-----------------|------------------------------|------------------|

| Instruction name                                                                       | ARM v8         | MIPS64                      | Power v3        | RISC-V                       | SPARC v.9        |

| Add word, immediate                                                                    | ADD, ADDI      | ADDU,<br>ADDUI,             | ADD, ADDI       | ADDW,<br>ADDWI               | ADD              |

| Add double word                                                                        | ADDX           | DADDU,<br>DADDUI            | ADD, ADDI       | ADD, ADDI                    | ADD              |

| Subtract                                                                               | SUB, SUBI      | SUBU, SUBI                  | SUBF            | SUBW,<br>SUBWI               | SUB              |

| Subtract double word                                                                   | SUBX           | DSUBU,<br>DSUBUI            | SUBF            | SUB,SUBI                     | SUB              |

| Multiply                                                                               | MUL, SMUL      | MUL, MULU,<br>DMUL, DMULU   | MULLW,<br>MullI | MUL, MULU,<br>MULW,<br>MULWU | MULX             |

| Divide                                                                                 | MULX,<br>SMULX | DIV,<br>DIVU,DDIV,<br>DDIVU | DIVW            | DIV, DIVU,<br>DIVW,<br>DIVWU | DIVX             |

| Remainder                                                                              |                | MOD, MODU,<br>DMOD, DMODU   | MODSW,<br>MODUW | REM, REMU,<br>REMW,<br>REMWU |                  |

| And                                                                                    | AND, ANDI      | AND, ANDI                   | AND, ANDI       | AND, ANDI                    | AND              |

| Or                                                                                     | OR, ORI        | OR, ORI                     | OR, ORI         | OR, ORI                      | OR               |

| Xor                                                                                    | XOR, XORI      | XOR, XORI                   | XOR, XORI       | XOR, XORI                    | XOR              |

| Load bits 3116                                                                         | MOV            | LUI                         | ADDIS           | ADDIS                        | SETHI<br>(Bfmt.) |

| Load upper bits of PC                                                                  | ADR            | ADDIUPC                     | ADDPCIS         | AUIPC                        |                  |

| Shift left logical, double<br>word and word versions,<br>immediate and variable        | LSL            | SLLV, SLL                   | RLWINM          | SLL, SLLI,<br>SLLW,<br>SLLWI | SLL              |

| Shift right logical, double<br>word and word version,<br>immediate and variables       | RSL            | SRLV, SRL                   | RLWINM<br>32-i  | SRL, SRLI,<br>SRLW,<br>SRLWI | SRL              |

| Shift right arithmetic,<br>double word and word<br>versions, immediate and<br>variable | RSA            | SRAV, SRA                   | SRAW            | SRA, SRAI,<br>SRAW,<br>SRAWI | SRA              |

| Compare                                                                                | СМР            | SLT/U, SL<br>TI/U           | CMP(I)CLR       | SLT/U,<br>SLTI/U             | SUBcc<br>r0,     |

K.2 A Survey of RISC Architectures for Desktop, Server, and Embedded Computers K-13

**Figure K.10** Desktop RISC arithmetic/logical instructions equivalent to RISC-V integer ISA. MIPS also provides instructions that trap on arithmetic overflow, which are synthesized in other architectures with multiple instructions. Note that in the "Arithmetic/logical" category all machines but SPARC use separate instruction mnemonics to indicate an immediate operand; SPARC offers immediate versions of these instructions but uses a single mnemonic. (Of course, these are separate opcodes!)

| K-14 |  | Appendix K | Survey of | Instruction | Set Architectures |

|------|--|------------|-----------|-------------|-------------------|

|------|--|------------|-----------|-------------|-------------------|

| Instruction name                 | ARMv8                | MIPS64                                                   | PowerPC                      | RISC-V                               | SPARC v.9                                        |

|----------------------------------|----------------------|----------------------------------------------------------|------------------------------|--------------------------------------|--------------------------------------------------|

| Branch on integer<br>compare     | B.cond,<br>CBZ, CBNZ | BEQ, BNE,<br>B_Z (<,<br>>,<br><=, >=)<br>OR<br>S***; BEZ | BC                           | BEQ, BNE,<br>BLT, BGE,<br>BLTU, BGEU |                                                  |

| Branch on floating-point compare | B.cond               | BC1T,<br>BC1F                                            | BC                           | BEZ, BNZ                             | <pre>FBPfcc (&lt;, &gt;, &lt;=, &gt;=, =,)</pre> |

| Jump, jump register              | B, BR                | J, JR                                                    | B, BCLR,<br>BCCTR            | JAL, JALR<br>(with x0)               | BA, JMPL<br>r0,                                  |

| Call, call register              | BL, BLR              | JAL,<br>JALR                                             | BL, BLA,<br>BCLRL,<br>BCCTRL | JAL, JALR                            | CALL, JMPL                                       |

| Trap                             | SVC, HVC,<br>SMC     | BREAK                                                    | TW, TWI                      | ECALL                                | Ticc, SIR                                        |

| Return from interrupt            | ERET                 | JR; ERET                                                 | RFI                          | EBREAK                               | DONE, RETRY,<br>RETURN                           |

Figure K.11 Desktop RISC control instructions equivalent to RV64G.

|                                                        | ARMv8                | MIPS64                   | PowerPC           | RISC-V                          | SPARC v.9                                   |

|--------------------------------------------------------|----------------------|--------------------------|-------------------|---------------------------------|---------------------------------------------|

| Number of condition code bits (integer and FP)         | 16 (8 + the inverse) | none                     | $8 \times 4$ both | none                            | $2 \times 4$<br>integer,<br>$4 \times 2$ FP |

| Basic compare instructions<br>(integer and FP)         | 1 integer; 1<br>FP   | 1 integer, 1 FP          | 4 integer, 2 FP   | 2 integer; 3 FP                 | 1 FP                                        |

| Basic branch instructions<br>(integer and FP)          | 1                    | 2 integer, 1 FP          | 1 both            | 4 integer (used for FP as well) | 3 integer,<br>1 FP                          |

| Compare register with register/<br>constant and branch | _                    | =, not=                  | _                 | =, not =, >=, <                 |                                             |

| Compare register to zero and branch                    |                      | =, not=, <, <=,<br>>, >= | _                 | =, not=, <, <=,<br>>, >=        | =, not=, <,<br><=, >, >=                    |

**Figure K.12** Summary of five desktop RISC approaches to conditional branches. Integer compare on SPARC is synthesized with an arithmetic instruction that sets the condition codes using r0 as the destination.

RISC-V and MIPS are most similar. RISC-V uses a compare and branch with a full set of arithmetic comparisons. MIPS also uses compare and branch, but the comparisons are limited to equality and tests against zero. This limited set of conditions simplifies the branch determination (since an ALU operation is not required to test the condition), at the cost of sometimes requiring the use of a set-on-less-than instruction (SLT, SLTI, SLTU, SLTIU), which compares two operands and then set the destination register to 1 if less and to 0 otherwise. Figure K.12 provides

| Floating point (instruc-<br>tion formats)                                                                                               | R-R              | R-R                 | R-R                | R-R                  | R-R             |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------|--------------------|----------------------|-----------------|

| Instruction name                                                                                                                        | ARMv8            | MIPS64              | PowerPC            | RISC-V               | SPARC v.9       |

| Add single, double                                                                                                                      | FADD             | ADD.*               | FADD*              | FADD.*               | FADD*           |

| Subtract single, double                                                                                                                 | FSUB             | SUB.*               | FSUB*              | FSUB.*               | FSUB*           |

| Multiply single, double                                                                                                                 | FMUL             | MUL.*               | FMUL*              | FMUL.*               | FMUL*           |

| Divide single, double                                                                                                                   | FDIV             | DIV.*               | FDIV*              | FDIV.*               | FDIV*           |

| Square root single, double                                                                                                              | FSQRT            | SQRT.*              | FSQRT*             | FSQRT.*              | FSQRT*          |

| Multiply add; Negative<br>multiply add: single,<br>double                                                                               | FMADD,<br>FNMADD | MADD.*<br>NMAD.*    | FMADD*,<br>FNMADD* | FMADD.*<br>FNMADD.*  |                 |

| Multiply subtract single,<br>double, Negative multiply<br>subtract: single, double                                                      | FMSUB,<br>FNMSUB | MSUB.*,<br>NMSUB.*  | FMSUB*,<br>FNMSUB* | FMSUB.*,<br>FNMSUB.* |                 |

| Copy sign or negative sign<br>double or single to another<br>FP register                                                                | FMOV,<br>FNEG    | FMOV.*, FNEG.*      | FMOV*,<br>FNEG*    | FSGNJ.*,<br>FSGNJN.* | FMOV*,<br>FNEG* |

| Replace sign bit with XOR of sign bits single double                                                                                    | FABS             | FABS.*              | FABS*              | FSGNJX.*             | FABS*           |

| Maximum or minimum single, double                                                                                                       | FMAX,<br>FMIN    | MAX.*, MIN.*        |                    | FMAX.*, FMIN.*       |                 |

| Classify floating point value single double                                                                                             |                  | CLASS.*             |                    | FCLASS.*             |                 |

| Compare                                                                                                                                 | FCMP             | CMP.*               | FCMP*              | FCMP.*               | FCMP*           |

| Convert between FP single<br>or double and FP single or<br>double, OR integer single<br>or double, signed and<br>unsigned with rounding | FCVT             | CVT, CEIL,<br>FLOOR |                    | FCVT                 | F*T0*           |

K.2 A Survey of RISC Architectures for Desktop, Server, and Embedded Computers K-15

**Figure K.13** Desktop RISC floating-point instructions equivalent to RV64G ISA with an empty entry meaning that the instruction is unavailable. ARMv8 uses the same assembly mnemonic for single and double precision; the register designator indicates the precision. "\*" is used as an abbreviation for S or D. For floating point compares all conditions: equal, not equal, less than, and less-then or equal are provided. Moves operate in both directions from/to integer registers. Classify sets a register based on whether the floating point quantity is plus or minus infinity, denorm, +/-0, etc.). The sign-injection instructions take two operands, but are primarily used to form floating point move, negate, and absolute value, which are separate instructions in the other ISAs.

additional details on conditional branch. RISC-V floating point comparisons sets an integer register to 0 or 1, and then use conditional branches on that content.MIPS also uses separate floating-point compare, which sets a floating point register to 0 or 1, which is then tested by a floating-point conditional branch.

ARM is similar to SPARC, in that it provides four traditional condition codes that are optionally set. CMP subtracts one operand from the other and the difference sets the condition codes. Compare negative (CMN) *adds* one operand to the other, and the sum sets the condition codes. TST performs logical AND on the two operands to set all condition codes but overflow, while TEQ uses exclusive OR to set the first three condition codes. Like SPARC, the conditional version of the ARM branch instruction tests condition codes to determine all possible unsigned and signed relations. ARMv8 added both bit-test instructions and also compare and branch against zero. Floating point compares on ARM, set the integer condition codes, which are used by the B.cond instruction.

As Figure K.13 shows the floating point support is similar on all five architectures.

#### RV64GC Core 16-bit Instructions

Figures K.14 through K.17 summarize the data transfer, ALU, and control instructions for our three embedded processors: microMIPS64, RV64GC, and Thumb-2. Since these architectures are all based on 32-bit or 64-bit versions of the full architecture, we focus our attention on the functionality implemented by the 16-bit instructions. Since floating point is optional, we do not include it. I

| Instruction name                                     | microMIPS64<br>rs1;rs2/dst; offset | RV64GC<br>rs1;rs2/dst; offset | Thumb-2<br>rs1;rs2/dst; offset |

|------------------------------------------------------|------------------------------------|-------------------------------|--------------------------------|

| Load word                                            | 8;8;4                              | 8;8;5                         | 8;8;5                          |

| Load double word                                     |                                    | 8;8;5                         |                                |

| Load word with stack pointer as base register        | 1;32;5                             | 1;32;6                        | 1;3;8                          |

| Load double word with stack pointer as base register |                                    | 1;32;6                        |                                |

| Store word                                           | 8;8;4                              | 8;8;5                         | 8;8;5                          |

| Store double word                                    |                                    | 8;8;5                         |                                |

| Store word with stack pointer as base register       | 1;32;5                             | 1;32;6                        | 1;3;8                          |

| Store double with stack pointer as base register     |                                    | 1;32;6                        |                                |

**Figure K.14** Embedded RISC data transfer instructions equivalent to RV64GC 16-bit ISA; a blank indicates that the instruction is not a 16-bit instruction. Rather than show the instruction name, where appropriate, we show the number of registers that can the base register for the address calculation, followed by the number of registers that can be the destination for a load or the source for a store, and finally, the size of the immediate used for address calculation. For example: 8; 8; 5 for a load means that there are 8 possible base registers, 8 possible destination registers for the load, and a 5-bit offset for the address calculation. For a store, 8; 8; 5, specifies that the source of the value to store comes from one of 8 registers. Remember that Thumb-2 also has 32-bit instructions (although not the full ARMv8 set) and that RV64GC and microMIPS64 have the full set of 32-bit instructions in RV64I or MIPS64.

| Instruction Name/Function                          | microMIPS64        | RV64GC                  | Thumb-2            |

|----------------------------------------------------|--------------------|-------------------------|--------------------|

| Load immediate                                     | 8;7                | 32;6                    | 8;8                |

| Load upper immediate                               |                    | 32;6                    |                    |

| add immediate                                      | 32;4               | 32;6                    | 8;8;3              |

| add immediate word (32 bits) & sign extend         |                    | 32;6                    |                    |

| add immediate to stack pointer                     | 1;9                | 1;6<br>(adds 16x imm.)  | 1;7                |

| add immediate to stack pointer store in reg.       | 1;8;6              | 1;8;6<br>(adds 4x imm.) |                    |

| shift left/right logical                           | 8;8;3 (shift amt.) | 8;6(shift amt.)         | 8;8;5 (shift amt.) |

| shift right arithmetic                             |                    | 8;6(shift amt.)         | 8;8;5 (shift amt.) |

| AND immediate                                      | 8;8;4              | 8;6                     | 8;8                |

| move                                               | 32;32              | 32;32                   | 16;16              |

| add                                                | 8;8;8              | 32;32                   | 8;8;8<br>16;16     |

| AND, OR, XOR                                       | 8;8                | 8;8                     | 8;8                |

| subtract                                           | 8;8;8              | 8;8                     | 8;8;8              |

| add word, subtract word (32 bits)<br>& sign extend |                    | 8;8                     |                    |

K.2 A Survey of RISC Architectures for Desktop, Server, and Embedded Computers K-17

**Figure K.15** ALU instructions provided in RV64GC and the equivalents, if any, in the 16-bit instructions of micro-MIPS64 or Thumb-2. An entry shows the number of register sources/destinations, followed by the size of the immediate field, if it exists for that instruction. The add to stack pointer with scaled immediate instructions are used for adjusting the stack pointer and creating a pointer to a location on the stack. In Thumb, the add has two forms one with three operands from the 8-register subset (Lo) and one with two operands but any of 16-registers.

|                                            | microMIPS64               | RV64GC                       | Thumb-2             |

|--------------------------------------------|---------------------------|------------------------------|---------------------|

| Unconditional branch                       | 10-bit offset             | 11-bit offset                | 11-bit offset       |

| Unconditional branch and link              |                           | 11-bit offset                | 11-bit offset       |

| Unconditional branch to register w/wo link | any of 32 registers       | any of 32 registers          |                     |

| Compare register to zero (=/!=) and branch | 8 registers; 7-bit offset | 8 registers; 8-bit<br>offset | no: but see caption |

**Figure K.16 Summary of three embedded RISC approaches to conditional branches.** A blank indicates that the instruction does not exist. Thumb-2 uses 4 condition code bits; it provides a conditional branch that tests the 4-bit condition code and has a branch offset of 8 bits.

#### K-18 Appendix K Survey of Instruction Set Architectures

| Function                              | Definition                                               | ARMv8                   | MIPS64             | PowerPC                                     | SPARC v.9 |

|---------------------------------------|----------------------------------------------------------|-------------------------|--------------------|---------------------------------------------|-----------|

| Load/store<br>multiple registers      | Loads or stores 2 or<br>more registers                   | Loadpair,<br>store pair |                    | Load store<br>multiple (<=31<br>registers), |           |

| Cache<br>manipulation and<br>prefetch | Modifies status of a<br>cache line or does a<br>prefetch | Prefetch                | CACHE,<br>PREFETCH | Prefetch                                    | Prefetch  |

**Figure K.17** Data transfer instructions not found in RISC-V core but found in two or more of the five desktop architectures. SPARC requires memory accesses to be aligned, while the other architectures support unaligned access, albeit, often with major performance penalties. The other architectures do not require alignment, but may use slow mechanisms to handle unaligned accesses.MIPS provides a set of instructions to handle misaligned accesses: LDL and LDR (load double left and load double right instructions) work as a pair to load a misaligned word; the corresponding store instructions perform the inverse. The Prefetch instruction causes a cache prefetch, while CACHE provides limited user control over the cache state.

# Instructions: Common Extensions beyond RV64G

Figures K.15 through K.18 list instructions not found in Figures K.9 through K.13 in the same four categories (data transfer, ALU, and control. The only significant floating point extension is the reciprocal instruction, which both MIPS64 and Power support. Instructions are put in these lists if they appear in more than one of the standard architectures. Recall that Figure K.3 on page 6 showed the address modes supported by the various instruction sets. All three processors provide more address modes than provided by RV64G. The loads and stores using these additional address modes are not shown in Figure K.17, but are effectively additional data transfer instructions. This means that ARM has 64 additional load and store instructions, while Power3 has 12, and MIPS64 and SPARVv9 each have 4.

To accelerate branches, modern processors use dynamic branch prediction (see Section 3.3). Many of these architectures in earlier versions supported delayed branches, although they have been dropped or largely eliminated in later versions

| Name             | Definition                                    | ARMv8 | MIPS64                                     | PowerPC             | SPARC v.9            |

|------------------|-----------------------------------------------|-------|--------------------------------------------|---------------------|----------------------|

| Delayed branches | Delayed branches<br>with/without cancellation |       | BEQ, BNE, BGTZ,<br>BLEZ, BCxEQZ,<br>BC×NEZ |                     | BPcc, A,<br>FPBcc, A |

| Conditional trap | Traps if a condition is true                  |       | TEQ, TNE, TGE,<br>TLT, TGEU, TLTU          | TW, TD,<br>TWI, TDI | Тсс                  |

**Figure K.18** Control instructions not found in RV64G core but found in two or more of the other architectures. MIPS64 Release 6 has nondelayed and normal delayed branches, while SPARC v.9 has delayed branches with cancellation based on the static prediction. of the architecture, typically by offering a nondelayed version, as the preferred conditional branch. The SPARC "annulling" branch is an optimized form of delayed branch that executes the instruction in the delay slot only if the branch is taken; otherwise, the instruction is annulled. This means the instruction at the target of the branch can safely be copied into the delay slot since it will only be executed if the branch is taken. The restrictions are that the target is not another branch and that the target is known at compile time. (SPARC also offers a nondelayed jump because an unconditional branch with the annul bit set does *not* execute the following instruction.).

In contrast to the differences among the full ISAs, the 16-bit subsets of the three embedded ISAs have essentially no significant differences other than those described in the earlier figures (e.g. size of immediate fields, uses of SP or other registers, etc.).

Now that we have covered the similarities, we will focus on the unique features of each architecture. We first cover the desktop/server RISCs, ordering them by length of description of the unique features from shortest to longest, and then the embedded RISCs.

#### Instructions Unique to MIPS64 R6

MIPS has gone through six generations of instruction sets. Generations 1–4 mostly added instructions. Release 6 eliminated many older instructions but also provided support for nondelayed branches and misaligned data access. Figure K.19 summarizes the unique instructions in MIPS64 R6.

| Instruction<br>class | Instruction name(s)                 | Function                                                                                                                                    |

|----------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| ALU                  | Byte align                          | Take a pair of registers and extract a word or double word of bytes.<br>Used to implement unaligned byte copies.                            |

|                      | Align Immediate to PC               | Adds the upper 16 bits of the PC to an immediate shifted left 16 bits and puts the result in a register; Used to get a PC-relative address. |

|                      | Bit swap                            | Reverses the bits in each byte of a register.                                                                                               |

|                      | No-op and link                      | Puts the value of PC+8 into a register                                                                                                      |

|                      | Logical NOR                         | Computes the NOR of 2 registers                                                                                                             |

| Control transfer     | Branch and Link conditional         | Compares a register to 0 and does a branch if condition is true; places the return address in the link register.                            |

|                      | Jump indexed, Jump and link indexed | Adds an offset and register to get new PC, w/wo link address                                                                                |

Figure K.19 Additional instructions provided MIPS64 R6. In addition, there are several instructions for supporting virtual machines, most are privileged.

#### Instructions Unique to SPARC v.9

Several features are unique to SPARC. We review the major figures and then summarize those and small differences in a figure.

#### **Register Windows**

The primary unique feature of SPARC is register windows, an optimization for reducing register traffic on procedure calls. Several banks of registers are used, with a new one allocated on each procedure call. Although this could limit the depth of procedure calls, the limitation is avoided by operating the banks as a circular buffer. The knee of the cost-performance curve seems to be six to eight banks; programs with deeper call stacks, would need to save and restore the registers to memory.

SPARC can have between 2 and 32 windows, typically using 8 registers each for the globals, locals, incoming parameters, and outgoing parameters. (Given that each window has 16 unique registers, an implementation of SPARC can have as few as 40 physical registers and as many as 520, although most have 128 to 136, so far.) Rather than tie window changes with call and return instructions, SPARC has the separate instructions SAVE and RESTORE. SAVE is used to "save" the caller's window by pointing to the next window of registers in addition to performing an add instruction. The trick is that the source register are from the caller's window. SPARC compilers typically use this instruction for changing the stack pointer to allocate local variables in a new stack frame. RESTORE is the inverse of SAVE, bringing back the caller's window while acting as an add instruction, with the source registers from the callee's window and the destination register in the caller's window. This automatically deallocates the stack frame. Compilers can also make use of it for generating the callee's final return value.

The danger of register windows is that the larger number of registers could slow down the clock rate. This was not the case for early implementations. The SPARC architecture (with register windows) and the MIPS R2000 architecture (without) have been built in several technologies since 1987. For several generations the SPARC clock rate has not been slower than the MIPS clock rate for implementations in similar technologies, probably because cache access times dominate register access times in these implementations. With the advent of multiple issue, which requires many more register ports, as will as register renaming or reorder buffers, register windows posed a larger penalty.Register windows were a feature of the original Berkeley RISC designs, and their inclusion in SPARC was inspired by those designs. Tensilica is the only other major architecture in use today employs them, and they were not included in the RISC-V ISA.

#### Fast Traps

SPARCv9 includes support to make traps fast. It expands the single level of traps to at least four levels, allowing the window overflow and underflow trap handlers to be interrupted. The extra levels mean the handler does not need to check for page faults or

misaligned stack pointers explicitly in the code, thereby making the handler faster. Two new instructions were added to return from this multilevel handler: RETRY (which retries the interrupted instruction) and DONE (which does not). To support user-level traps, the instruction RETURN will return from the trap in nonprivileged mode.

#### Support for LISP and Smalltalk